オープンソースのISAとして注目を集め始めているRISC-V、ハードでLinuxのような革命が起こせるのかと期待されています。

RISC-Vはオープンソースでコードも公開されているため、誰でもFPGAにRISC-Vコアをビルドして動作させることができます。

前回、開発環境を構築してXilinx Artix FPGAを搭載したDigilentのArty A7ボード用にFPGAとサンプルプログラムをビルドしました。

今回は、Xilinx Artix FPGAを搭載したDigilentのArty A7ボードに実際に書き込みます。

準備

環境構築前の準備

必要なもの

Digilent Arty A7

Xilinx Artix A7を搭載したDigilentの開発ボードです。

Olimex

ARM-USB-TINY-H JTAGアダプタです。デバッグで必要となります。

ジャンパケーブル

Arty A7とOlimexを接続するために使用します。

端の茶色から使用すると、色が合うため配線の時に楽です。

ケーブルの作成

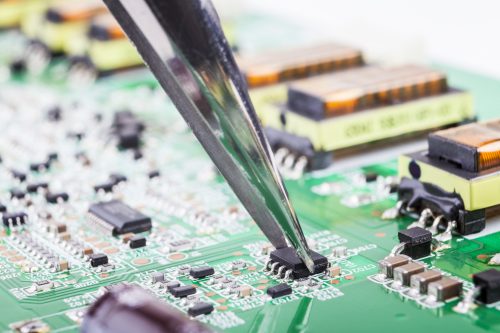

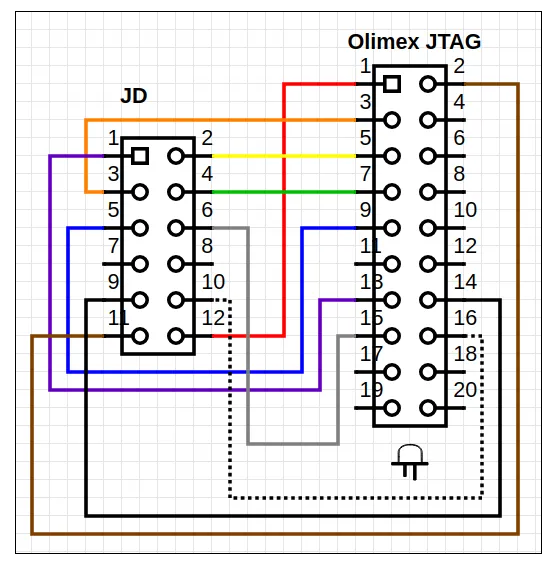

ジャンパケーブルを使ってOlimexとArty A7 FPGAボードを接続します。

Arty A7 ボードコネクタ

| 1 | TDO | TDI | 2 |

| 3 | nTRST | TMS | 4 |

| 5 | TCK | nRST | 6 |

| 7 | 8 | ||

| 9 | GND | GND | 10 |

| 11 | VREF | VREF | 12 |

Olimex ARM-USB-TINY-H

| 1 | VREF | VREF | 2 |

| 3 | nTRST | 4 | |

| 5 | TDI | 6 | |

| 7 | TMS | 8 | |

| 9 | TCK | 10 | |

| 11 | 12 | ||

| 13 | TDO | GND | 14 |

| 15 | nRST | GND | 16 |

| 17 | 18 | ||

| 19 | 20 |

写真は参考にした「Digikey Digilent Arty A7 with Xilinx Artix-7 Implementing SiFive FE310 RISC-V(英文)」のものです。

RISC-V FPGAの書き込み前準備

ドライバのインストール

UbuntuはWindowsとは異なり、ドライバがVivadoインストール時にインストールされないため、別途インストールが必要。

Vivadoインストールディレクトリ配下にあるinstall_driversを実行することでドライバーがインストールされます。

cd /home/user/riscv/tool/Xilinx/Vivado/2019.1/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers # 以下、コマンド実行結果 INFO: Installing cable drivers. INFO: Script name = ./install_drivers INFO: HostName = user INFO: Current working dir = /home/user/riscv/tool/Xilinx/Vivado/2019.1/data/xicom/cable_drivers/lin64/install_script/install_drivers INFO: Kernel version = 5.0.0-25-generic. INFO: Arch = x86_64. Successfully installed Digilent Cable Drivers --File /etc/udev/rules.d/52-xilinx-ftdi-usb.rules does not exist. --File version of /etc/udev/rules.d/52-xilinx-ftdi-usb.rules = 0000. --Updating rules file. --File /etc/udev/rules.d/52-xilinx-pcusb.rules does not exist. --File version of /etc/udev/rules.d/52-xilinx-pcusb.rules = 0000. --Updating rules file. INFO: Digilent Return code = 0 INFO: Xilinx Return code = 0 INFO: Xilinx FTDI Return code = 0 INFO: Return code = 0 INFO: Driver installation successful. CRITICAL WARNING: Cable(s) on the system must be unplugged then plugged back in order for the driver scripts to update the cables.

udevルール作成

デバイスは,コンピュータに接続された各種周辺機器のことを指します。

lsusbで接続しているデバイスを確認できます。下の例は不要なものを削除しています。実際はより多くのデバイスが表示されるはずです。

今回USBで接続するデバイスは、2つ。

・Olimex Debug Adapter

・Arty A7

user@user:~/riscv/freedom-e-sdk$ lsusb Bus 002 Device 006: ID 0403:6010 Future Technology Devices International, Ltd FT2232C Dual USB-UART/FIFO IC Bus 001 Device 004: ID 15ba:002a Olimex Ltd. ARM-USB-TINY-H JTAG interface

Linuxはデバイスを「デバイスファイル」という特殊なファイルとして認識します。

デバイスファイルを通じて入出力を行うようになっています。

udevのルールファイルを書いておくと、デバイスファイルを動的に作成、削除できるようになります。

lsusbで確認したベンダーIDとプロダクトIDを設定します。

sudo nano /etc/udev/rules.d/99-openocd.rules

# 下記を記載

# For Arty 7 board

SUBSYSTEM=="tty", ATTRS{idVendor}=="0403",ATTRS{idProduct}=="6010", MODE="664", GROUP="plugdev"

SUBSYSTEM=="usb", ATTR{idVendor}=="0403",ATTR{idProduct}=="6010", MODE="664", GROUP="plugdev"

# For Olimex debug adapter

SUBSYSTEM=="tty", ATTRS{idVendor}=="15ba",ATTRS{idProduct}=="002a", MODE="664", GROUP="plugdev"

SUBSYSTEM=="usb", ATTR{idVendor}=="15ba",ATTR{idProduct}=="002a", MODE="664", GROUP="plugdev"

Olimex ARM-USB-TINY-H JTAGアダプタを接続し、正しく設定できたか確認します

user@user:~/riscv/freedom-e-sdk$ ls -lha /dev/ttyUSB* crw-rw-r-- 1 root plugdev 188, 0 8月 24 10:26 /dev/ttyUSB0 crw-rw-r-- 1 root plugdev 188, 1 8月 24 10:22 /dev/ttyUSB1 crw-rw-r-- 1 root plugdev 188, 2 8月 24 09:24 /dev/ttyUSB2

機器の接続

Vivadoを使ってFPGAに書き込む前に機器を以下のように接続します。

・UART通信・電源供給

J10のUSBコネクタとPCをマイクロUSBケーブルで接続します。電源もUSB経由で供給されます。

・FPGAプログラミング・デバッグ

Olimex ARM-USB-TINY-H JTAGアダプタとPCをUSBケーブルで接続します。自作したケーブルはArty A7ボードのJDコネクタに接続しておきます。

Vivadoを使ったRISC-V FPGAの書き込み

Vivadoを使ってFPGAデータの書き込み

FPGAの書き込みには2種類あります。

・FPGAに直接bitファイルを書き込む方法

・Flashメモリにmcsファイルを書き込み、FPGAに転送する方法。

FPGAに直接書き込む方法では、電源を切るとFPGAのデータは消失してしまうために、mcsをFlashメモリに書き込む方法を解説します。

Vivado 2019.1を開きます。

Flowから「Open Hardware Manager」を選択します。

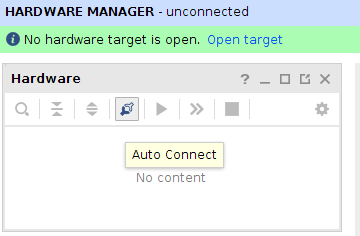

Open TargetをクリックしてAuto Connectを選択してください。

もしくは、Hardwareパネルの「Auto Connect」ボタンをクリックします。

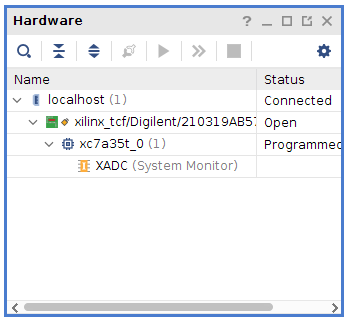

成功すると以下のようにデバイスが表示されます。

出てこない場合は、ドライバーがインストールされているか確認してください。

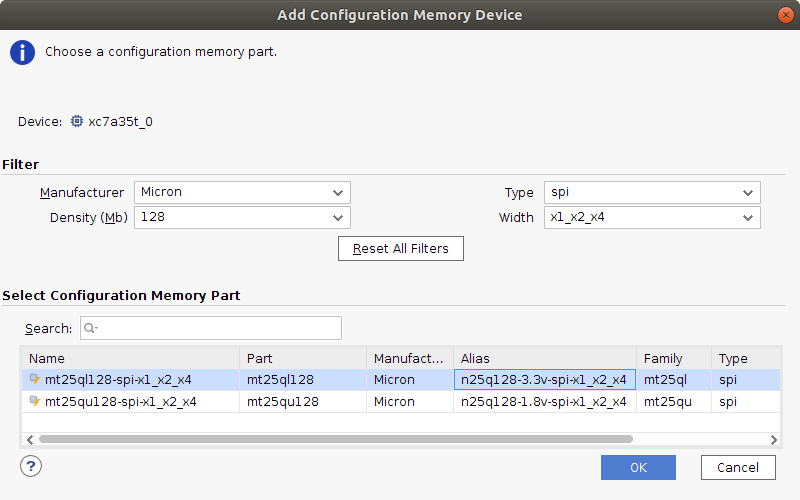

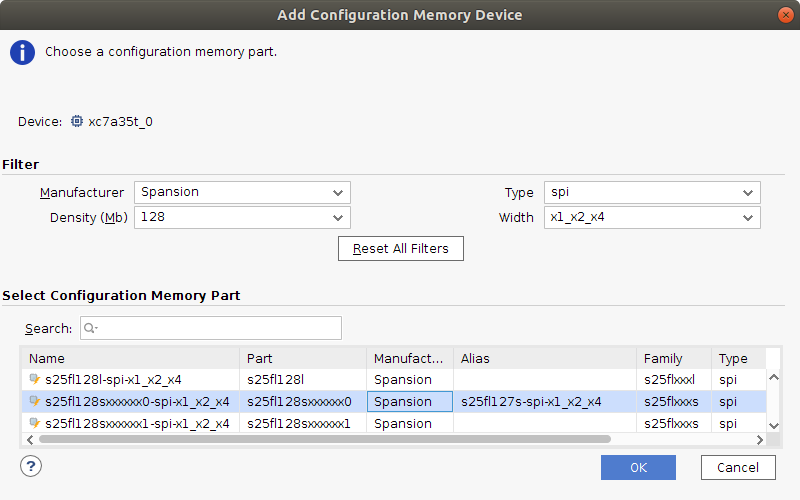

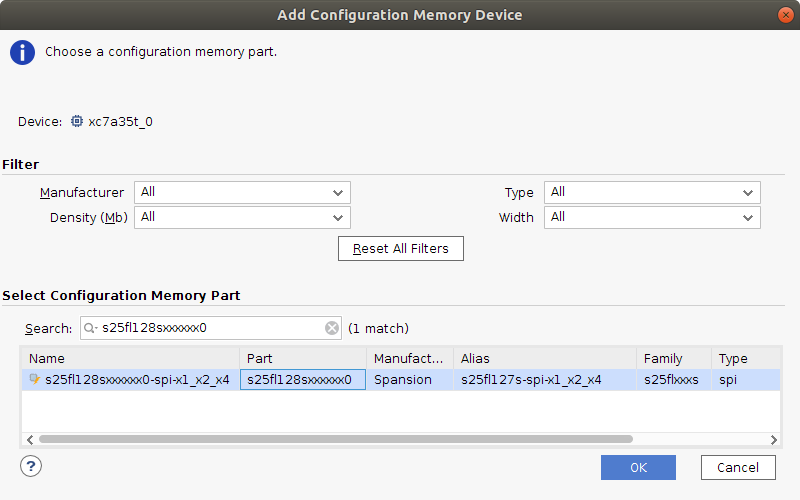

Auto connectで表示されたデバイス(ICのマーク)を右クリックして「Add Configuration Memory Device」を選択して、FLASHメモリを選択します。

| 35T | 100T | |

| Manufacturer | Micron | Spansion |

| Density(Mb) | 128 | 128 |

| Type | spi | spi |

| Width | x1_x2_x4 | x1_x2_x4 |

| Alias | n25q128-3.3v-spi-x1_x2_x4 | n25fl127s-spi-x1_x2_x4 |

Artix A7 35Tの設定画面

Artix A7 100Tの設定画面

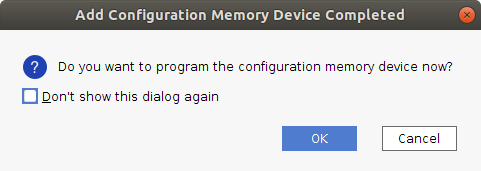

コンフィグレーションファイルを書き込むか聞かれますので、OKを選択してください。

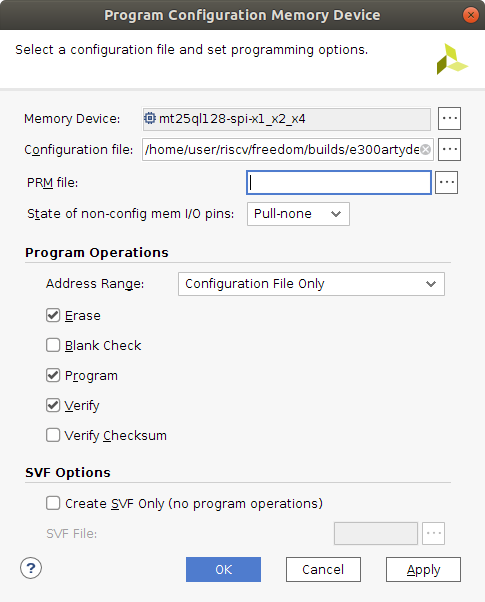

メモリを右クリックして、「Program Configration Memory Device」を選択することで、いつでも書き込むことができます。

Configuration fileには、ビルド編で作成したmcsファイルを選択します。

/home/user/riscv/freedom/builds/e300artydevkit/obj/E300ArtyDevKitFPGAChip.mcs

Artix A7 35Tの設定画面

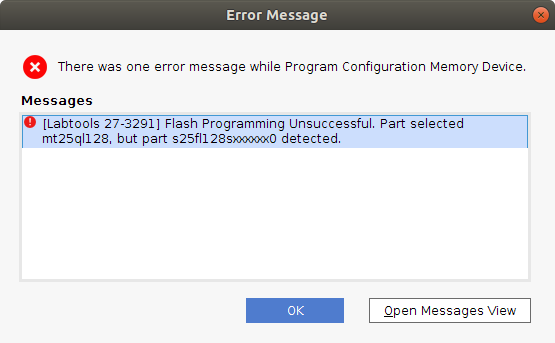

もし以下のように設定したメモリと別のメモリを検出したというエラーが発生した場合、メモリの設定を変更してください。ボードの版数によって、搭載されているメモリが異なる可能性があります。

ハードウェアパネルの追加されたメモリを右クリックして「Remove Configuration Memory Device」を選択してメモリ設定を削除します。

おそらくボードの版数によってメモリが異なるのだと思われます。

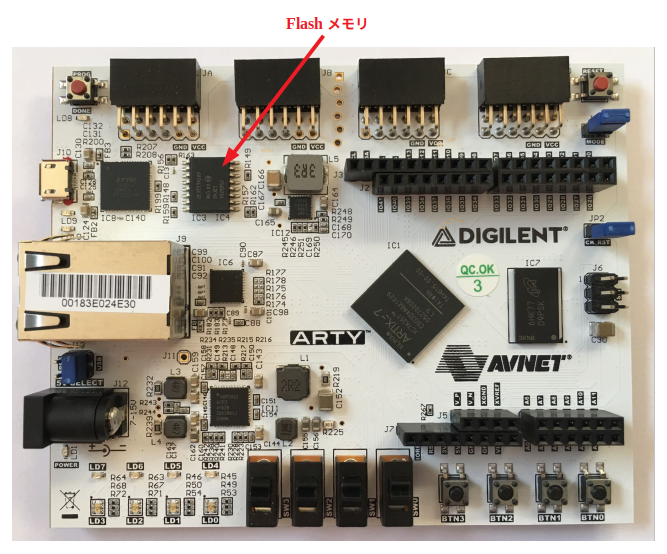

USBコネクタの横にFTDIのICがありますがその横にあるのがFLASHメモリです。

よく見るとMicronとかSpansionとか書いていると思います。確認してみてください。

エラー時に指摘されたメモリで検索して設定してください。

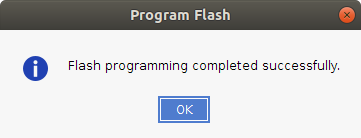

書き込みに成功すると、成功メッセージが表示されます。

ボード上のPROGボタンを押すと、メモリ上のコンフィグデータがArtix-7 FPGAへの書き込みを開始します。

PROGスイッチ横のDONE LEDが点灯すると完了です。

LEDの4,5,6が点灯していれば正常に書き込みができています。

参照

・Digilent Arty A7 with Xilinx Artix-7 Implementing SiFive FE310 RISC-V

・SiFive Core IP FPGA Eval Kit User Guidev3p0

まとめ

RISC-VをVivadoとFreedom-e-sdkを用いて、実際にArty A7 FPGAボードに書き込む方法をまとめました。

この他にもFreedom Studioを用いた方法もあるので、今度まとめたいと思います。

長くなったので、ソフトの書き込みは別の記事にしたいと思います。

RISC-Vに興味がある方はこの本を読んでみてください。

著者は、RISC-Vに実際に参画しているCPUアーキテクチャの権威 パターソン先生です。